THCS251_Rev.3.01_E

Copyright©2023 THine Electronics, Inc. THine Electronics, Inc.

2/33

SC: E

Contents page

General description..................................................................................................................................................1

Application..............................................................................................................................................................1

Features ...................................................................................................................................................................1

Block diagram.........................................................................................................................................................1

1. Pin configuration.............................................................................................................................................3

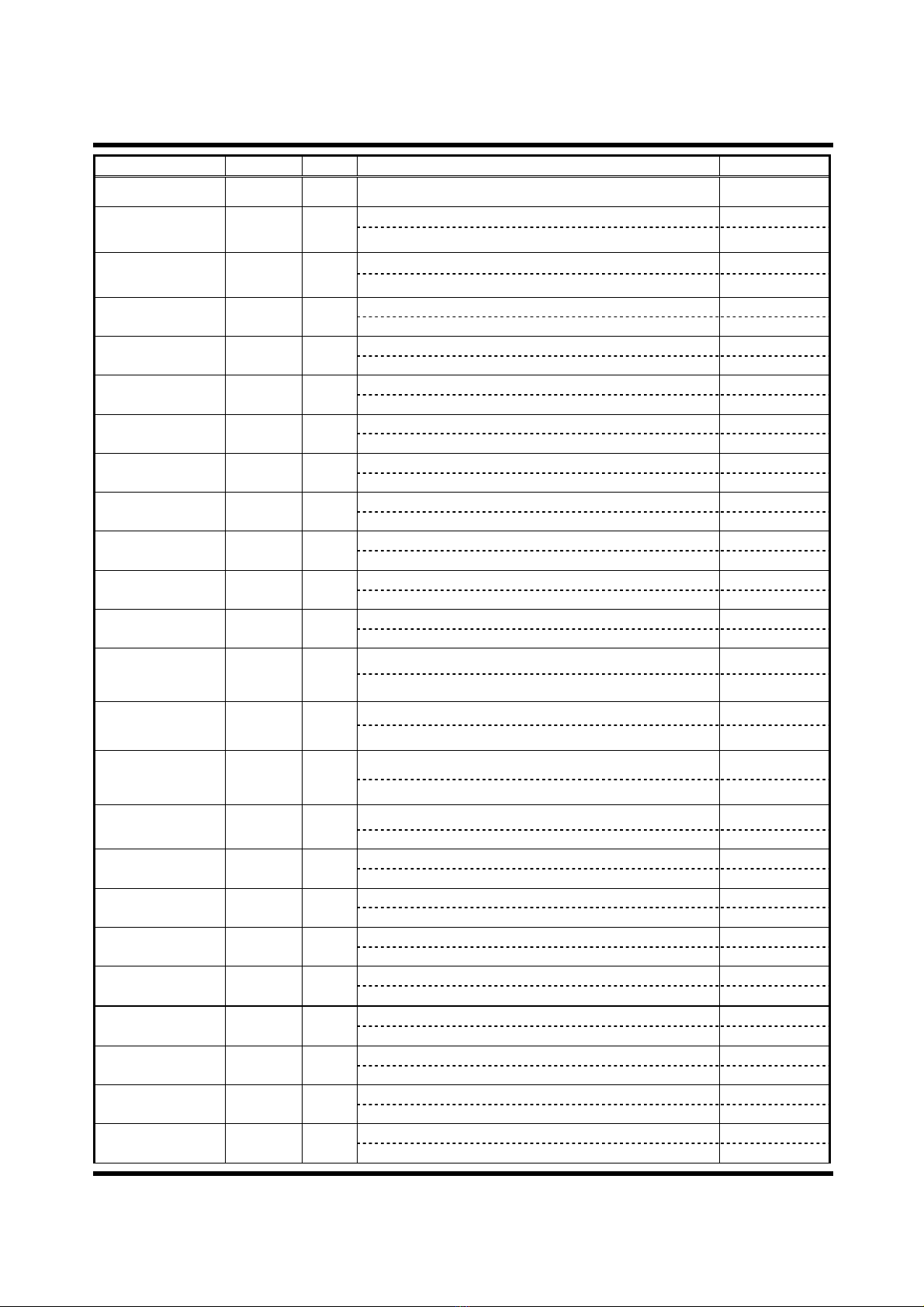

2. Pin description.................................................................................................................................................4

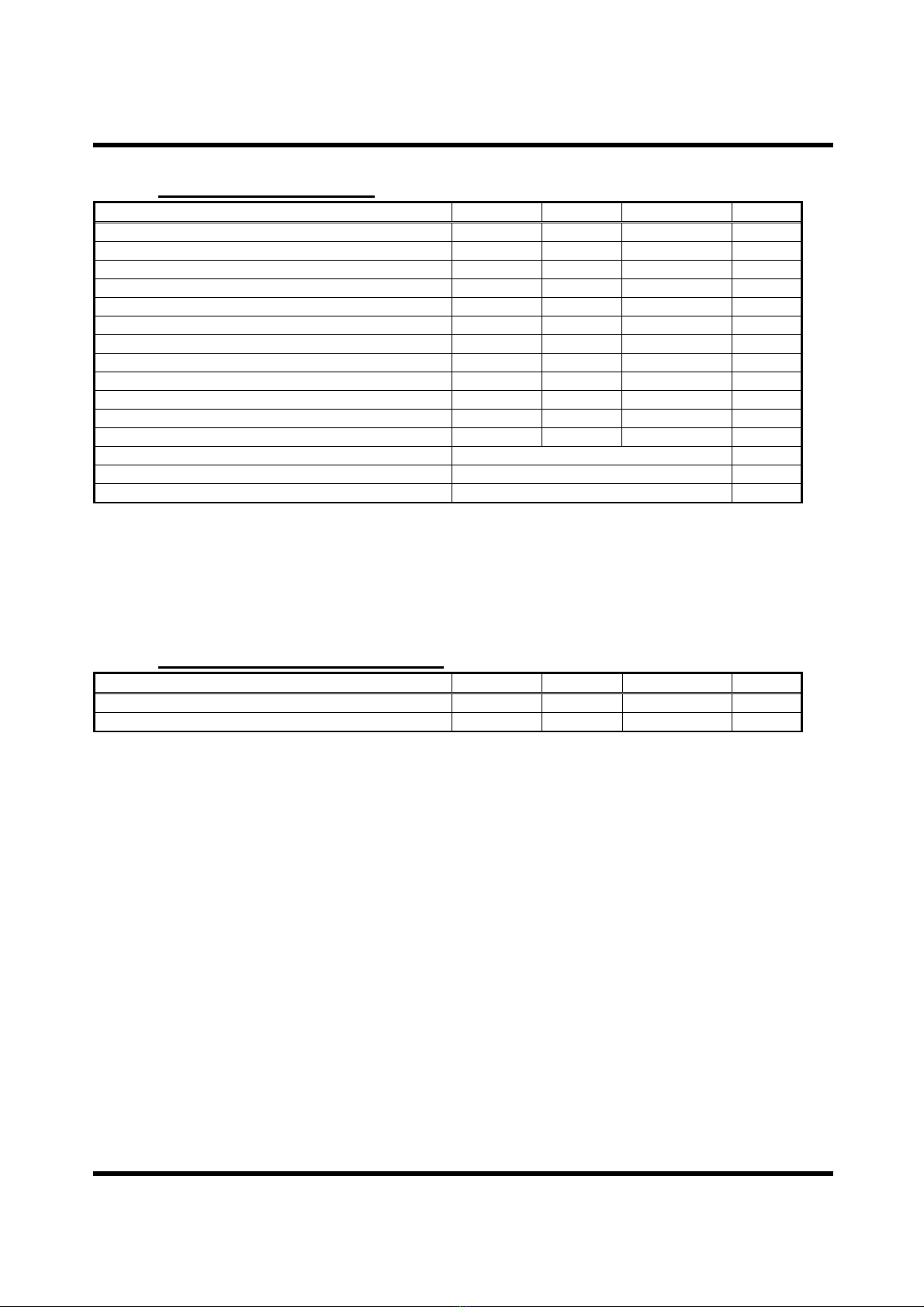

3. Absolute maximum ratings..............................................................................................................................8

4. Recommended operating conditions ...............................................................................................................8

5. Electrical characteristics..................................................................................................................................9

5.1. Current consumption...............................................................................................................................9

5.2. LVCMOS/Analog input DC specifications ...........................................................................................10

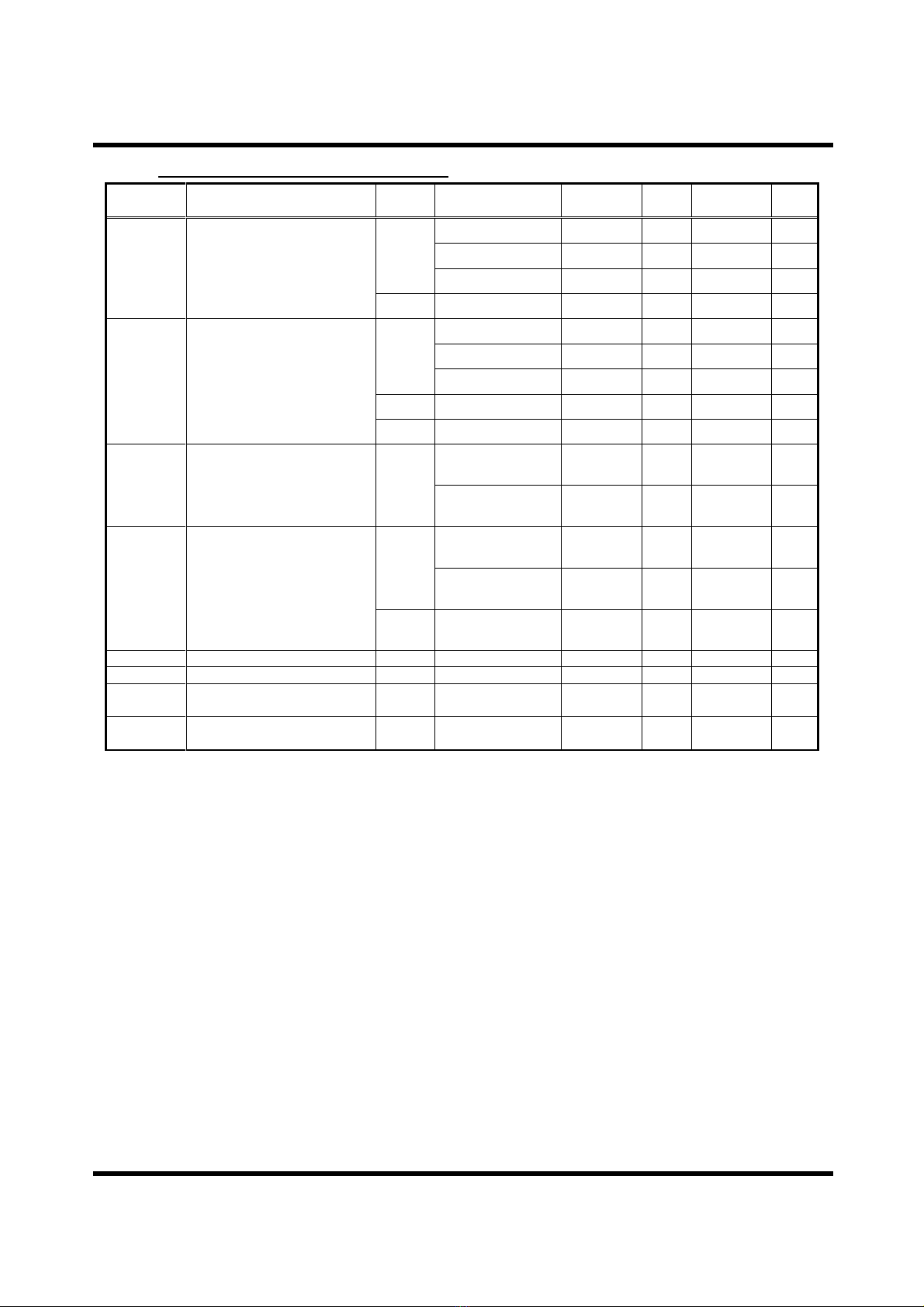

5.3. LVCMOS AC characteristics................................................................................................................. 11

5.4. CML DC characteristics........................................................................................................................14

5.5. CMLAC characteristics ........................................................................................................................14

6. CML Line Eye diagrams ...............................................................................................................................19

6.1. CML output Eye diagrams.....................................................................................................................19

6.2. CML input Eye diagrams ......................................................................................................................20

7. Function.........................................................................................................................................................21

7.1. Functional overview..............................................................................................................................21

7.2. Power supply.........................................................................................................................................21

7.2.1. Internal regulator output/input function (CAPOUT, CAPINA, CAPINP) ....................................21

7.3. Operating mode.....................................................................................................................................21

7.4. Transmission mode................................................................................................................................22

7.4.1. Full duplex Bi-directional transmission mode...............................................................................22

7.4.2. Unidirectional transmission mode.................................................................................................24

7.5. IO configuration ....................................................................................................................................25

7.5.1. Input and Output digital noise filter ..............................................................................................25

7.5.2. LVCMOS output buffer type configuration...................................................................................25

7.5.3. 5V Tolerant I/O..............................................................................................................................25

7.6. Sampling clock configuration................................................................................................................26

7.6.1. Sampling clock selection...............................................................................................................26

7.6.2. Spread Spectrum Clock Generator (SSCG) and REFIN frequency...............................................28

7.7. Error detection and indication...............................................................................................................29

7.8. Standby mode........................................................................................................................................30

8. Package..........................................................................................................................................................31

Notices and Requests.............................................................................................................................................32